-

조합회로와 순차회로전공/논리회로실험 2020. 6. 10. 14:21

* 모든 사진 파일은 부경대학교 한영선 교수님의 PPT에서 발췌했습니다. 주소 : http://hpcl.pknu.ac.kr

조합회로(Combinational Circuit)

일정 시점의 출력값이 일정 시점의 입력값에 의해서만 결정되는 논리회로다.

뭔가 '조합'회로라는 명칭 자체가 이전 상태와 현재 상태의 '조합'으로 이루어질 것 같지만 아니다!

조합회로는 값을 저장하는 능력이 없다.

값을 저장하는 건 순차회로다.

조합회로의 예시는 Adder, Subtractor, Compapator, Decoder, Encoder, (De)Multiplexer, ... 등이 있다.

full adder는 carry를 입력값으로 쓴다. Comparator

A<B, A=B, A>B 에 따라 출력값 결정하는 조합회로

Decoder

적은 입력으로 많은 출력을 생성하는 조합회로. 2^INPUT = OUTPUT

진리표가 조금 어색하다.

Encoder

많은 입력으로 적은 출력을 생성하는 조합회로. INPUT = 2^OUTPUT

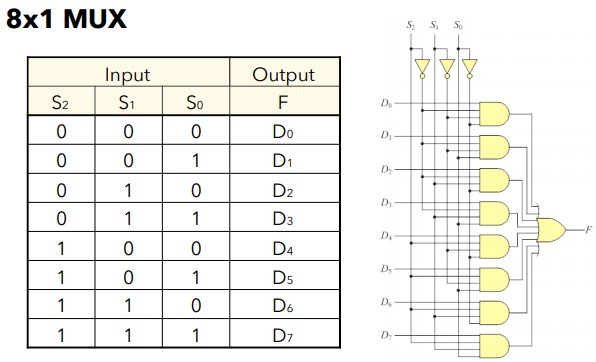

MUX(Multiplexer)

여러 입력 중 하나를 선택하여 출력하는 회로이다.

회로 중에서 유일하게 Verilog 실습시 아무것도 못했던 부분이다.

아직도 익숙하지는 않은데, 그 이유가 Select Signal이라는 개념을 처음 접해서 그런 듯하다.

아래의 그림처럼 8x1 Mux일때는 직관적으로 8개의 입력에 1개의 출력이 들어간다.

그리고 Selector Signal을 8개의 입력을 수용할 수 있게 3비트로 구성을 한다.

그리고 Selector Signal 값에 따라 8개의 입력 중 하나를 출력한다.

이정도면 과거의 내가 이해할 수 있겠지? ㅎ

DEMUX(Demultiplexer)

하나의 입력으로 여러 개의 출력을 결과로 내놓는 회로

예시와 같이 1x8 DEMUX일 때, Select Signal 값에 의해 어떤 출력선을 고를지가 결정된다.

출력값은 입력값인 X가 된다.

순차회로(Sequential Circuit)

현재 출력이 '이전' 상태(=이전 사이클의 결과)와 현재 입력값에 의해 결정되는 논리 회로이다.

조합회로에 기억 기능이 추가된 회로다.

순차회로는 클럭 신호에 의해 상태가 변화하는 동기 회로와 비동기 회로로 나뉜다.

동기회로

클럭 신호로 상태가 바뀌는 회로다.

비동기회로

클럭 신호 이외의 요소로 상태가 바뀌는 회로다.

주기적으로 들어오는 클럭 신호가 없으니 동기 회로에 비해 전력이 덜 소모되는 장점이 있다.

둘 중 어떤 회로를 쓰는지는 용도에 따라 결정한다.

순차회로의 필수 구성요소

(1) 클럭 신호

클럭은 일정 주기로 0과 1을 반복한다.

그림에서의 Duty Cycle이란, 클럭이 high, 즉 1일 때가 전체 주기를 기준으로 얼마나 존재하는지를 표현하는 용어다.

즉, duty cycle이 높을수록 활성화된 신호의 비율이 많다는 뜻이다.

duty cycle의 퍼센트별 예시 (2) 플립플롭(메모리 기능)

동기 회로를 위한 1bit짜리 기억 소자이다.

교수님께서는 D플립플롭이 가장 많이 쓰인다고 이것만 공부하라고 하셨다.

플립플롭은 클럭이 1일 때와 0일 때 작동하지 않는다.

0에서 1, 1에서 0으로 바뀌는 '순간'에 작동을 한다.

이걸 '엣지'라고 하는데, 0에서 1로 바뀔 땐 'positive edge', 1에서 0으로 바뀔 땐 'negative edge'라고 한다.

위의 그림은 클럭이 0에서 1로 바뀔 때 값을 인식하는 'positive edge'이다.

빨간 타원 부분인 순간에만 D 플립플롭의 값을 받아 출력이 결정된다.

첫 엣지에서는 D값이 0이므로 출력은 0이 된다.

두번째 엣지에서는 D값이 1이므로 다시 출력은 1로 된다.

이렇게 클럭, D플립플롭, 출력 세 그래프가 있을 때 positive edge인지, negative edge인지 파악할 수 있어야 한다.

그리고 출력 Q를 살펴보면 처음 시작이 1이다. 이렇게 시작하는 값을 leading edge value라 하고

trailing edge value는 끝나는 값이다.

왼쪽은 D래치이고 오른쪽은 D플립플롭이다.

래치는 클럭이 0과 1일 때 반응한다(=Level Triggered)는 차이점을 기억해두면 된다.

Verilog로 D플립플롭 코드를 작성할 때 어려웠다.

그 이유가 D값과 클럭값을 어떻게 설정해야될지 몰랐는데 그냥 입력값만 넣으면 되었다.

그리고 시간에 따른 변화값을 어떻게 코드로 녹여낼까 도무지 감이 잡히지 않았는데 생각해보니

시뮬레이션을 매 주기마다 할 때 값을 일일이 바꾸면 되었다..

negative reset 코드 암기 아직 NRST 이해못함

(3) 상태 변화(상태 머신)

얘는 다음 시간에 배울 듯.

Propagation Delay

입력 신호가 주어진 후, 출력이 변할 때까지의 시간

경로가 가장 긴 경로를 Critical Path라고 한다.

Critical Path가 Propagation Delay를 결정하게 된다. 얘가 제일 늦으니까.

화살표 너비만큼의 시간이 지난 뒤 출력 Q의 값이 상승하는 모습 D플립플롭 값은 클럭펄스의 주기보다 엇박자로 값을 줘야 한다.

클록펄스와 D플립플롭값이 일치한다면, 어떤 값을 저장할지 결정할 수 없기 때문이다.

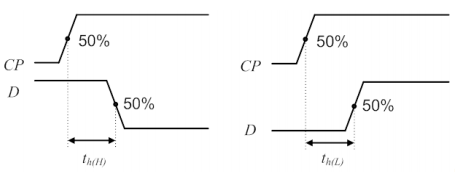

그리고 클럭의 앞뒤로 D플립플롭의 값을 유지시켜줘야 안전하게 값이 저장된다.

클럭을 기준으로 앞 시간을 Setup Time, 뒤를 Hold Time이다.

Setup Time

Hold Time Maximum Clock Frequency

회로가 정상적으로 동작하기 위한 최대 주파수이다.

회로는 Maximum Clock Frequency 내에서 동작해야 한다.

'전공 > 논리회로실험' 카테고리의 다른 글

Verilog 문법, 특징 요약 (0) 2020.06.09